## 1. Using a Nonlinear NMOS Transistor for Amplification

Earlier in the semester, we learned about how transistors can be modeled as a switch, with resistors and capacitors, which allows us to think about how to use transistors for logic circuits. Another important use of transistors is with amplification, and the op-amps we use consist of transistors behaving as amplifiers. This topic is explored more in future circuits classes, but in this discussion, we will start to explore how we can use linearization to model a transistor amplifier circuit.

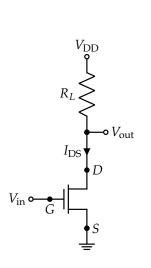

Consider the following schematic where  $V_{\text{DD}} = 1.5 \text{ V}$ ,  $R_L = 400 \Omega$  and the NMOS transistor has threshold voltage  $V_{\text{th}} = 0.2 \text{ V}$ . We are interested in analyzing the response of this circuit to input voltages of the form  $V_{\text{in}}(t) = V_{\text{in,DC}} + v_{\text{in,AC}}(t)$ , where  $V_{\text{in,DC}}$  is some constant voltage and  $v_{\text{in,AC}}(t) = 0.001 \cos(\omega t) \text{ V}$  is a sinusoidal signal whose magnitude is much smaller than  $V_{\text{in,DC}}$ .

The I-V relationship of an NMOS can be modeled as non-linear functions over different regions of operation. For simplicity, let's just focus on the case when  $0 \le V_{\text{GS}} - V_{\text{th}} < V_{\text{DS}}$  (this is known as the saturation region because the current is approximately constant with respect to  $V_{\text{DS}}$ , the voltage between the drain and source terminals of the NMOS transistor, but this is out of scope). For this regime of interest, the I-V relationship model we will use is given by

$$I_{\rm DS}(V_{\rm GS}) = \frac{K}{2} (V_{\rm GS} - V_{\rm th})^2$$

(1)

where *K* is a constant that depends on the NMOS transistor size and properties.

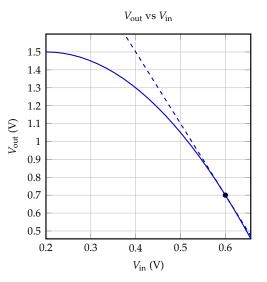

**(b)**  $V_{\text{out}}$  vs  $V_{\text{in}}$  in the regime of interest. Tangent is drawn at the operating point  $V_{\text{in,DC}} = 0.6$  V,  $V_{\text{out,DC}} = 0.7$  V

From Ohm's law and KCL, we know that

(a) NMOS Transistor circuit

$$V_{\rm out}(t) = V_{\rm DD} - R_L I_{\rm DS}(t).$$

<sup>(2)</sup>

Note from Figure 1a that  $V_{in} = V_{GS}$  and  $V_{out} = V_{DS}$ . In Figure 1b, we can see the curve of  $V_{out}$  vs  $V_{in}$  in the transistor operating regime of interest.

(a) Using eq. (1) and eq. (2), express  $V_{out}(t)$  as a function of  $V_{in}(t)$  symbolically. (You can use  $V_{DD}$ ,  $R_L$ ,  $V_{in}$ , K,  $V_{th}$  in your answer.)

(b) We can decompose the input into constant (i.e., DC) and time-varying (i.e., AC) components to obtain  $V_{in}(t) = V_{in,DC} + v_{in,AC}(t)$ . Find  $\frac{dV_{out}}{dV_{in}}$  at  $V_{in} = V_{in,DC}$  in terms of  $R_L$  and  $g_m$ , where  $g_m = K(V_{in,DC} - V_{th})$  is known as the transconductance gain of the transistor at the provided operating point. Use this to linearize  $V_{out}(t)$  as a function of  $V_{in}(t)$  about  $V_{in} = V_{in,DC}$ .

(c) Next, we can also decompose the output V<sub>out</sub> into DC and AC components to obtain V<sub>out</sub>(t) = V<sub>out,DC</sub> + v<sub>out,AC</sub>(t). What can we define as V<sub>out,DC</sub> from the linearized representation in part 1.b? Assuming that V<sub>out</sub>(t) ≈ V<sub>out</sub>(t) (which occurs when v<sub>in,AC</sub>(t) is small), what is the linear approximation for v<sub>out,AC</sub>(t)? (HINT: V<sub>out,DC</sub> is a constant value.)

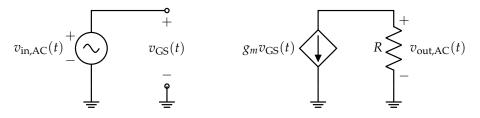

(d) We can create a small signal model for the NMOS transistor amplifier with the following circuit:

Using the approximation for  $v_{out,AC}(t)$  from the previous part, calculate the resistance value *R* of the resistor in the small signal model shown above.

## **Contributors:**

- Anish Muthali.

- Vladimir Stojanovic.

- Moses Won.

- Ayan Biswas.

- Nikhil Jain.

- Chancharik Mitra.